24位高性能模数转换器ME9620应用经验与总结

应用的高分辨率ADC虽可提供更大的可用带宽,但偏移与漂移指标远低于工业ADC的需求。ME9620将两种类型的

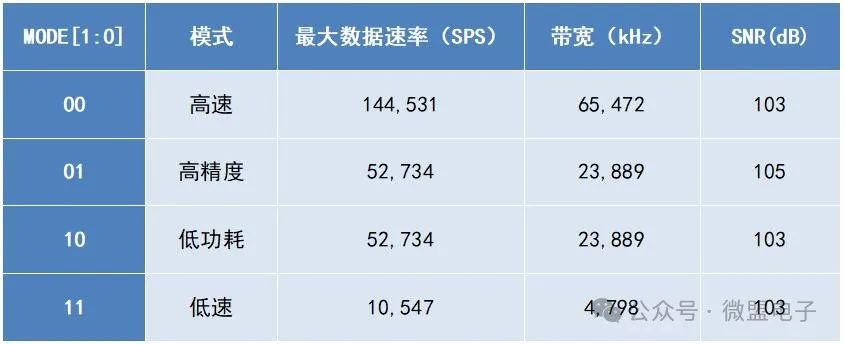

ME9620内部集成有多个独立的高阶斩波稳定调制器和FIR数字滤波器,可实现4/8通道同步采样,支持高速、高精度、低功耗、低速4种工作模式。ME9620可通过设置相应的输入/输出引脚选择工作模式,无需寄存器编程,其数据输出可选串行SPI或FRAME-SYNC接口,便于连接至DSPFPGA微控制器。每个接口均支持菊花链,可满足规定的要求严格的多通道信号采集应用,如振动分析、医疗监控、声学系统、动态应变测量及压力测量设备等。

建议每个电源引脚处均需放置一个10uF钽电容和0.1uF陶瓷电容。ME9620严格要求电源稳定,不可与其它易造成电源不稳定的器件共用电源。

ME9620的8个ADC通道支持差分信号输入。为了不发生溢出,请保证差分输入范围不大于参考电压范围。输入信号的共模理论上支持从0到AVDD电平的范围,但为了尽可能发挥ADC的性能,同时能提高信号幅度,建议将输入共模配置在AVDD/2附近的电平。

芯片输出的VCOM信号作为ADC内部工作的共模电平,需要外置稳压电容保证其电压稳定,可在片外连接一个缓冲器后的输出作为ME9620输入差分信号的共模电平使用,以保证芯片内外信号电路共模的一致性。

为了简化应用,建议VREFN连接到AGND。为了能够更好的保证ADC性能不受参考源的影响,应用时需要在片外通过一个高精度低噪声稳压参考源产生VREFP电压,并在VREFP与VREFN管脚两端挂接1uF以上量级的稳压陶瓷电容。

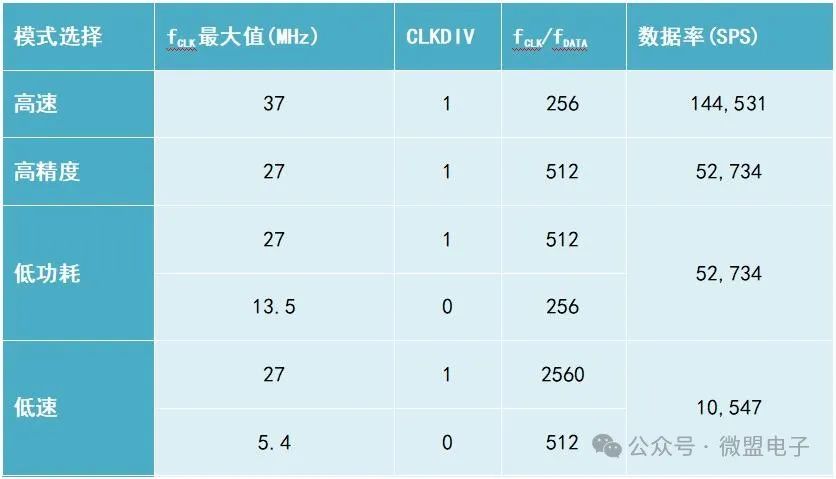

ME9620必须有时钟输入才能运行。外部时钟频率(fCLK)的选择不会影响其分辨率。

当为高速模式时,fCLK最大可为37MHz,其他三种模式时,最大输入时钟为27MHz。且当fCLK>

27MHz时,只能采用FRAME-SYNC方式读取数据。

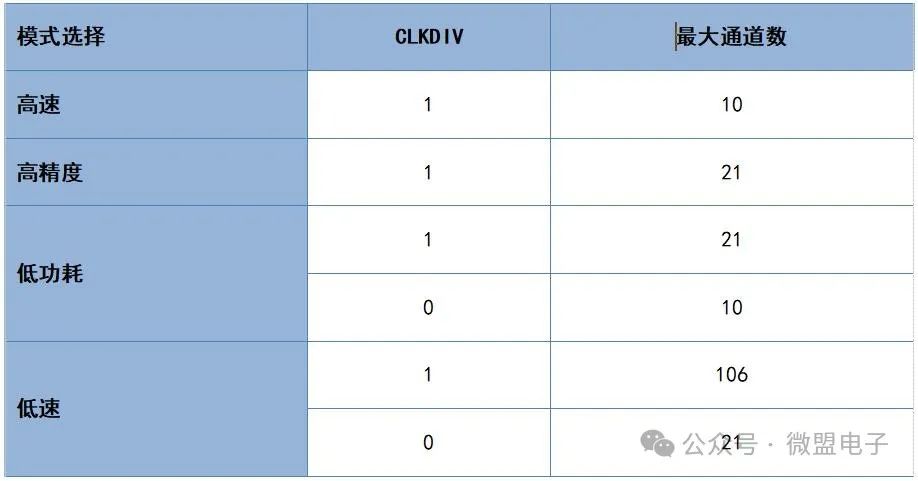

ME9620的数据输出率与fCLK具有固定的比例关系,且低功耗、低速模式下,CLKDIV能够对fCLK分频。另外两种模式下,CLKDIV必须为1,具体关系如下表所示:

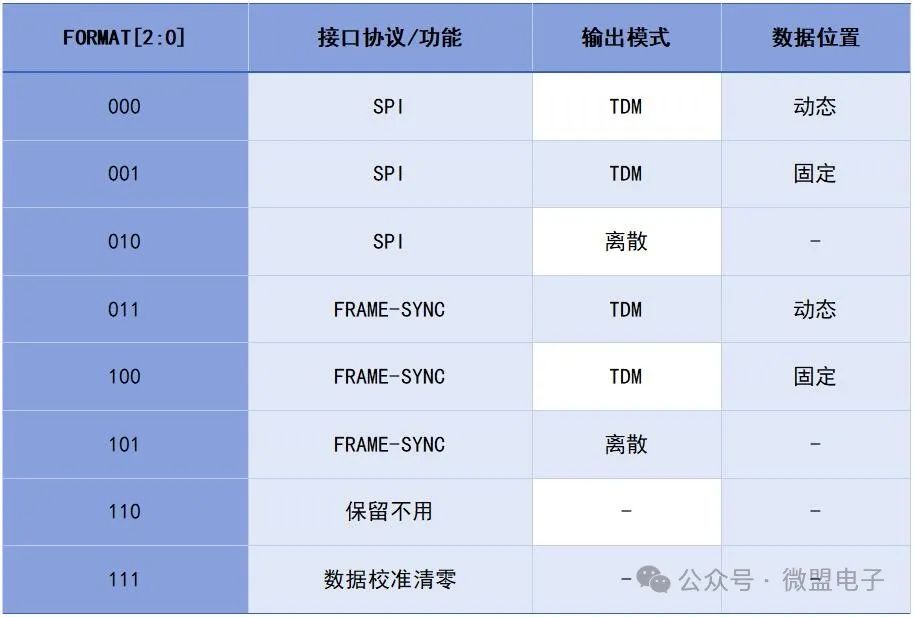

转换后的数据输出采用串行接口,可采用两种接口协议:SPI协议或FRAME-SYNC协议,同时也可选不一样的数据输出格式(TDM/离散、固定/动态数据位置)。协议和数据输出格式的选择是由引脚FORFMAT[2:0]控制,如下表所示:

数据对应SPI和FRAME-SYNC接口协议,或者通过各自的通道DOUT引脚以并行数据格式(离散模式)移位输出,或者所有通道的数据以串行格式通过公共引脚DOUT1(TDM 模式)移位输出。

TDM表示8个通道数据全部由DUOT1输出,CH1在前,CH8在后。此时若数据位置为“动态”则表示:若某通道关闭,则该通道仍然输出,输出数据为0;若数据位置为“固定”,则如果某通道关闭,该通道不输出,直接输出下一通道数据。

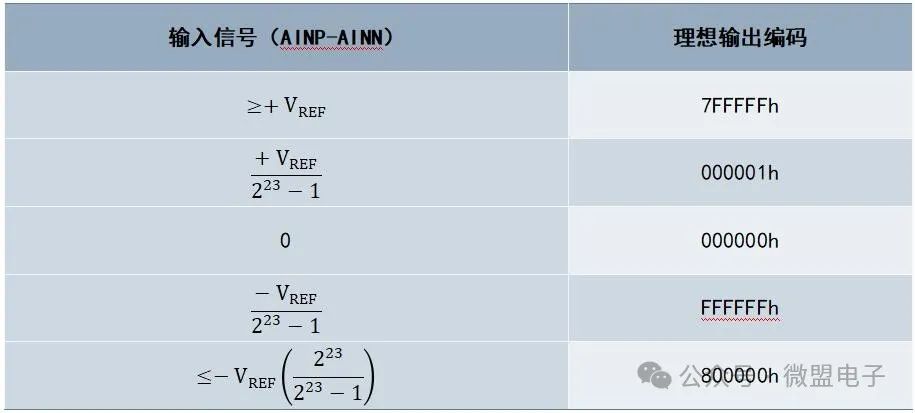

ME9620输出数据位宽为24位,正满量程为7FFFFFh,负满量程为800000h,理想输出码与输入信号关系如下表所示:

引脚拉低后,再将引脚返回高电平来实现同步。当引脚变为低电平时,转换过程停止。当

引脚返回高电平时,转换过程重新开始。由于ME9620转换器以相同的主时钟并行运行并使用相同的

输入控制,因此它们始终相互同步。但是,多个器件的同步有些不同。在器件上电时,器件之间内部复位的变化可能会导致转换时序的不确定性。

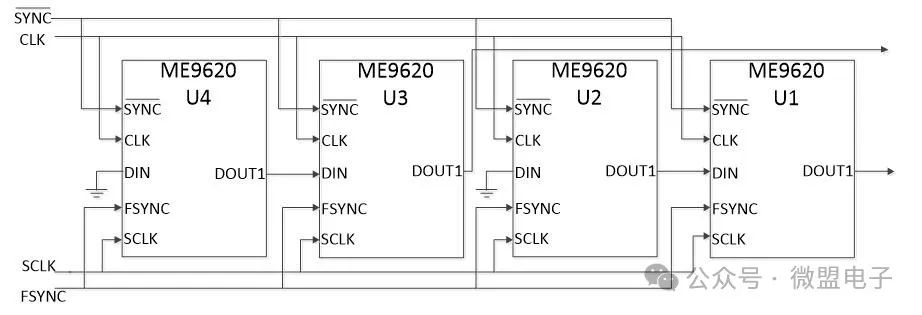

多个ME9620可以以菊花链方式连接在一起,以在单个引脚上输出数据。一个器件的DOUT1 数据输出引脚连接到下一个器件的DIN,如下图所示。

以这种方式来进行菊花链连接的最大通道数受fSCLK频率、模式选择和CLKDIV的限制。fSCLK的频率必须充足高,以能够在一个fDATA周期内将数据从所有通道中完全移出。下表列出了fSCLK = fCLK时菊花链通道的最大数量。

2)数字输入脚需要串接50Ω电阻,并放置在数字驱动源末端(靠近ME9620)。

3)模拟电路(输入脚)走线必须远离数字电路(输入脚)并防止产生走线)模拟信号输入端必须接驱动,

走线短而直,且远离数字信号线。AINP和AINN之间需接1~10nF电容。6)电源、模拟输入、参考输入的去耦电容必须尽可能的靠近ME9620。7)时钟线Ω电阻。要求晶振必须稳定。

采样保持放大器(SHA)和片内基准电压源。该产品采用多级差分流水线架构,具有输出纠错逻辑

方面实现新的突破,可提供卓越的速度与精度,扩展了其PulSAR产品系列。在当今大多数

EVAL-AD7172-4SDZ,评估套件采用AD7172-4,这是一款

LTC2440资料下载内容主要介绍了:LTC2440功能和特点LTC2440引脚功能LTC2440内部方框图LTC2440典型应用电路图

(ADC)的基础原理是什么?常用的几种ADC类型的基础原理及特点是什么?

(ADC),内置片内采样保持电路,专对于低成本、低功耗、小尺寸和易用性而设计。

IC ADC 8BIT MONO W/CLOCK 18CDIPLX高端AD

。板载组件包括高精度,缓冲带隙5V基准电压源(ADR435),基准电压缓冲

应用,只需+5 V电源和一个编码时钟就可以实现60 MSPS采样速率和10

科技有限公司, AD9208BBPZRL-3000 是一款双通道、14

和采样保持电路,确保实现较低的功耗、较小的封装尺寸和出色的易用性。该产品

(ADC),内置片内采样保持电路,具有低成本、低功耗、小尺寸和易于使用等特性。它采用105 MSPS

(ADC),内置片内采样保持电路,具有低成本、低功耗、小尺寸和易于使用等特性。它采用105 MSPS

(ADC),内置片内采样保持电路,专对于低成本、低功耗、小尺寸和易用性而设计。该产品的

采样保持放大器和基准电压源。它采用多级差分流水线架构,内置输出纠错逻辑,在20/40/65 MSPS数据速率时可提供12

采样保持放大器和一个基准电压源。它采用多级差分流水线架构,内置输出纠错逻辑,在最高65 MSPS数据速率

采样保持放大器和基准电压源。它采用多级差分流水线架构,内置输出纠错逻辑,在65 MSPS数据速率

、易于使用等优点。它内置8个通道,每通道包含一个低噪声前置放大器(LNA)的可变增益放大器(VGA)、一个抗混叠滤波

(ADC),内置一个片内采样保持电路,专对于低成本、低功耗、小尺寸和易用性进行了优化。该产品采用100 MSPS

。每个通道均可以独立工作。产品型号; AD9288BSTZ-100产品名称:

产品介绍AD9410BSVZ询价热线BSVZ代理王先生*** 深圳市首质诚科技有限公司AD9410BSVZ是一款10

、小尺寸和易用性进行了优化。 该产品的采样速率高达100 MSPS,具有出众的信噪比(SNR),适合采用基带中频(

、80 MSPS/105 MSPS/125 MSPS/ 150 MSPS

(ADC),旨在支持需要低成本、小尺寸且具多功能性的通信应用。这款双通道ADC

、80 MSPS/105 MSPS/125 MSPS/ 150 MSPS

(ADC),旨在支持需要低成本、小尺寸且具多功能性的通信应用。这款双通道ADC

ADC0809更详细的参数说明能查看它的芯片手册(英文原版)链接:文章目录1、ADC0809

文章目录1. ADC1. ADCADC(Analog-to-digital converters,

LTC2452。输入是双极性的,具有Ref-to Ref +范围。该调制

的专有采样技术将平均输入电流降低至比典型Δ-ΣADC低50nA的数量级。 LTC2452采用8引脚,3x2mm DFN封装,具有易于使用的SPI接口

。GC1808支持主、从机和两种串行音频数据格式。GC1808支持掉电和时钟

信号处理解决方案供应商,AD7989-1和AD7989-5 PulSAR

WM8738是WolfsonMicroelectronics plc公司研制的一个为消费电子应用的

广泛用于需要高信号完整度和电气隔离的电机驱动应用。虽然Σ-Δ技术本身已广为人知,但

使用常常存在不足,无法释放这种技术的全部潜力。本文从应用角度考察Σ-Δ ADC,并讨论如何在电机驱动中实现最佳

InterADC的主要特征是速度快,这是所有类型中最快的。采样率能够达到1GSPS以上。但是,由于功率和音量

EVAL-AD7172-2SDZ,评估套件采用AD7172-2,这是一款低功耗,

Delta Sigma ADC。 LTC2412是一款双通道差分输入微功耗

进行了仿真,同时对系统中的某些关键参数进行了修改,分析了参数变化对系统的影响。

之间均可),如有需要可搭配一些外围电路。使用上的要求:前端为 CMOS线阵传感

ADS1230 ADS1230 是一种高精度 20

指标、系统工作原理和模拟与数字工作原理。本文承接上文,主要介绍 ADS1210在使用

信号大小。而输出的数字量则表示输入信号相对于参考信号的大小。 线封装。创新三角洲西格玛

时间: 2024-03-30

时间: 2024-03-30  作者:

作者: